TMS320C6657CZHA IC DSP FIX/FLOAT POINT 625FCBGA

Parametru di u produttu

Descrizzione

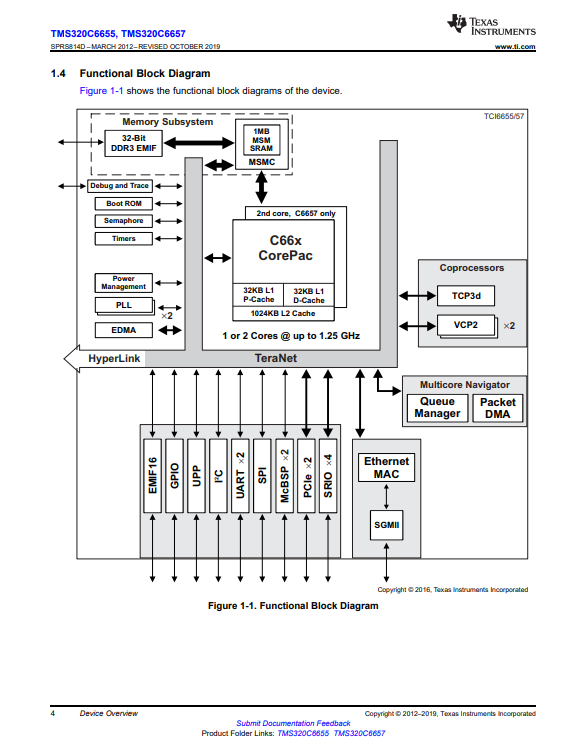

L'architettura KeyStone di TI furnisce una piattaforma programabile chì integra diversi sottosistemi (core C66x, sottosistema di memoria, periferiche è acceleratori) è utilizza parechji cumpunenti è tecniche innovatori per maximizà a cumunicazione intradispositiva è interdispositiva chì permette à e diverse risorse DSP di operare in modu efficiente è senza saldatura.Cintrali à sta architettura sò cumpunenti chjave cum'è Multicore Navigator chì permette una gestione di dati efficiente trà e diverse cumpunenti di u dispositivu.TeraNet hè un tissu di switch senza bloccu chì permette un muvimentu di dati interni rapidu è senza disputa.U controller di memoria spartutu multicore permette l'accessu à a memoria spartuta è esterna direttamente senza sguassate da a capacità di a tela di u switch.Per l'usu di u puntu fissu, u core C66x hà 4 × a capacità di multiplicazione (MAC) di i core C64x +.Inoltre, u core C66x integra capacità in virgola flottante è a prestazione computazionale bruta per core hè un 40 GMACS per core è 20 GFLOPS per core (@frequenza operativa 1.25 GHz).U core C66x pò eseguisce 8 operazioni MAC in virgola flottante di precisione unica per ciclu è pò eseguisce operazioni di precisione doppia è mista è hè conforme à IEEE 754.U core C66x incorpora 90 novi struzzioni (paragunatu à u core C64x +) destinati à l'elaborazione orientata à a virgola flottante è a matematica vettoriale.Questi miglioramenti rendenu miglioramenti di rendiment considerablemente in i kernels DSP populari utilizati in funzioni di trasfurmazione di signali, matematiche è acquisizione di l'imaghjini.U core C66x hè compatibile cù codice retrocede cù i nuclei DSP C6000 di a generazione precedente di TI fissi è flottanti, assicurendu a portabilità di u software è i cicli di sviluppu di u software accurtati per l'applicazioni chì migranu à un hardware più veloce.U C665x DSP integra una grande quantità di memoria in chip.In più di 32KB di prugramma L1 è cache di dati, 1024KB di memoria dedicata pò esse cunfigurata cum'è RAM o cache mape.U dispusitivu integra ancu 1024KB di Multicore Shared Memory chì pò esse usatu cum'è L2 SRAM spartutu è / o L3 SRAM spartutu.Tutte e memorie L2 incorporanu a rilevazione di l'errore è a correzione d'errore.Per un accessu rapidu à a memoria esterna, stu dispusitivu include una interfaccia di memoria esterna DDR-3 32-bit (EMIF) chì funziona à una freccia di 1333 MHz è hà supportu ECC DRAM.

| Specificazioni: | |

| Attributu | Valore |

| categuria | Circuiti integrati (IC) |

| Embedded - DSP (processori di signali digitale) | |

| Mfr | Texas Instruments |

| Serie | TMS320C66x |

| Pacchettu | vassa |

| Status di parte | Attivu |

| Tipu | Puntu Fissu / Flotante |

| Interfaccia | DDR3, EBI/EMI, Ethernet, McBSP, PCIe, I²C, SPI, UART, UPP |

| Frequenza di u Clock | 1 GHz |

| Memoria non volatile | ROM (128 kB) |

| RAM On-Chip | 2,06 MB |

| Tensione - I/O | 1.0V, 1.5V, 1.8V |

| Tensione - Core | 1,00 V |

| Temperature di funziunamentu | -40 °C ~ 100 °C (TC) |

| Tipu di muntatura | Munti superficia |

| Pacchettu / Casu | 625-BFBGA, FCBGA |

| Paquet di Dispositivi Fornitore | 625-FCBGA (21x21) |

| U numeru di produttu di basa | TMS320 |

RelativuPRODOTTI

-

Tel

-

E-mail

-

skype

-

whatsapp

whatsapp