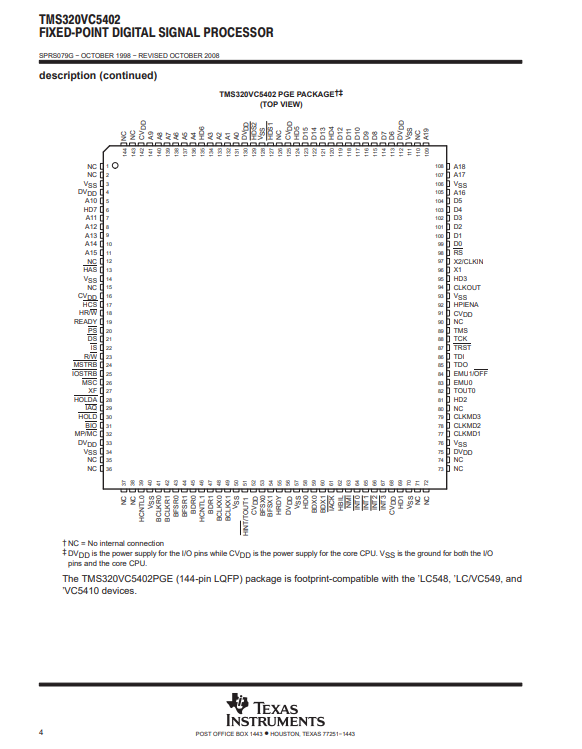

TMS320VC5402PGE100 IC DIG SIG PROCESSOR 144-LQFP

Parametru di u produttu

Descrizzione

U TMS320VC5402, u processatore di segnali digitale (DSP) (in seguitu chjamatu 5402, salvu altrimenti specificatu) hè basatu annantu à una architettura avanzata di Harvard modificata chì hà un bus di memoria di prugramma è trè bus di memoria di dati.Stu processore furnisce una unità logica aritmetica (ALU) cun un altu gradu di parallelismu, logica hardware specifica per l'applicazione, memoria in chip, è periferiche supplementari in chip.A basa di a flessibilità operativa è a velocità di stu DSP hè un set di struzzioni altamente specializate.U prugramma separatu è i spazii di dati permettenu l'accessu simultaneu à l'urdinamentu di u prugramma è i dati, furnisce l'altu gradu di parallelismu.Dui operazioni di lettura è una operazione di scrittura ponu esse realizate in un unicu ciclu.Istruzzioni cù magazzini paralleli è struzzioni specifiche per l'applicazione ponu aduprà pienamente sta architettura.Inoltre, i dati ponu esse trasferiti trà spazii di dati è prugrammi.Un tali parallelismu sustene un putente inseme di operazioni aritmetiche, logiche è di manipulazione di bit chì ponu esse realizati in un ciculu di una sola macchina.Inoltre, u 5402 include i miccanismi di cuntrollu per gestisce interruzioni, operazioni ripetute è chjama di funzione.

| Specificazioni: | |

| Attributu | Valore |

| categuria | Circuiti integrati (IC) |

| Embedded - DSP (processori di signali digitale) | |

| Mfr | Texas Instruments |

| Serie | TMS320C54x |

| Pacchettu | vassa |

| Status di parte | Attivu |

| Tipu | Puntu Fissu |

| Interfaccia | Interfaccia host, McBSP |

| Frequenza di u Clock | 100 MHz |

| Memoria non volatile | ROM (8 kB) |

| RAM On-Chip | 32 kB |

| Tensione - I/O | 3,30 V |

| Tensione - Core | 1,80 V |

| Temperature di funziunamentu | -40 °C ~ 100 °C (TC) |

| Tipu di muntatura | Munti superficia |

| Pacchettu / Casu | 144-LQFP |

| Paquet di Dispositivi Fornitore | 144-LQFP (20x20) |

| U numeru di produttu di basa | TMS320 |

RelativuPRODOTTI

-

Tel

-

E-mail

-

skype

-

whatsapp

whatsapp