OMAPL138EZWTD4 IC MPU OMAP-L1X 456MHZ 361NFBGA

Parametru di u produttu

Descrizzione

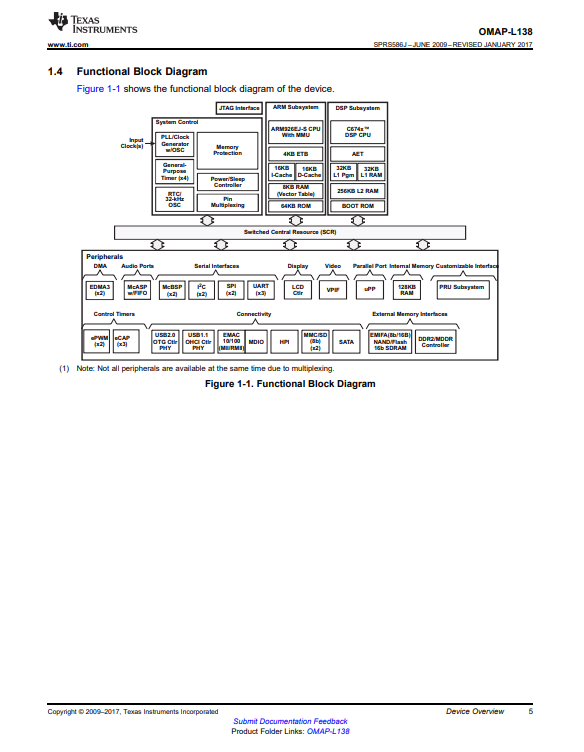

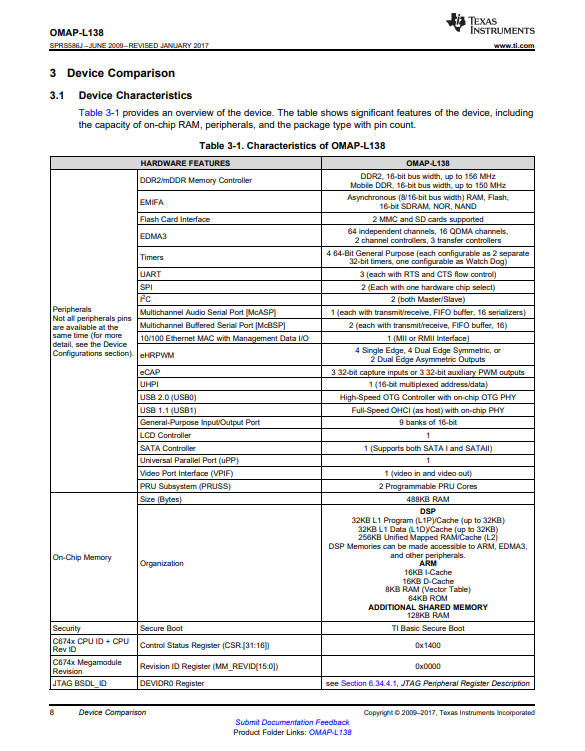

U processore OMAP-L138 C6000 DSP+ARM hè un processore di applicazioni di bassa putenza basatu annantu à un core ARM926EJ-S è C674x DSP.Stu processore furnisce una putenza significativamente più bassa cà l'altri membri di a piattaforma TMS320C6000™ di DSP.U dispusitivu permette à i fabbricanti di l'equipaggiu originale (OEM) è à i fabricatori di cuncepimentu originale (ODM) di portà rapidamente à u mercatu i dispositi cù sistemi operativi robusti, interfacce d'utilizatore ricche è prestazioni elevate di processore attraversu a massima flessibilità di una soluzione di processore mistu cumplettamente integrata.L'architettura dual-core di u dispusitivu furnisce benefizii sia di e tecnulugia di DSP sia di tecnulugii di computer set di istruzzioni ridotti (RISC), chì incorporanu un core TMS320C674x DSP d'altu rendiment è un core ARM926EJ-S.L'ARM926EJ-S è un core di processore RISC a 32 bit che esegue istruzioni a 32 o 16 bit ed elabora dati a 32, 16 o 8 bit.U core usa pipelining per chì tutte e parte di u processore è u sistema di memoria ponu operare continuamente.U core ARM9 hà un coprocessore 15 (CP15), un modulu di prutezzione, è unità di gestione di memoria di dati è di prugramma (MMU) cù buffers di tavulinu.U core ARM9 hà struzzioni separati 16-KB è cache di dati 16-KB.E duie cache sò associative in 4 vie cù tag virtuale di indice virtuale (VIVT).U core ARM9 hà ancu 8KB di RAM (Vector Table) è 64KB di ROM.U core DSP di u dispositivu usa una architettura basata in cache à 2 livelli.A cache di u prugramma di livellu 1 (L1P) hè una cache di mappa diretta di 32 KB, è a cache di dati di livellu 1 (L1D) hè una cache di 32 KB in 2 vie, set-associative.A cache di u prugramma di livellu 2 (L2P) hè custituita da un spaziu di memoria di 256 KB chì hè spartutu trà u prugramma è u spaziu di dati.A memoria L2 pò esse cunfigurata cum'è memoria mappata, cache, o cumminazzioni di i dui.Ancu se u DSP L2 hè accessibile da l'ARM9 è altri ospiti in u sistema, un 128KB addiziale di memoria RAM sparta hè dispunibule per l'utilizazione da altri ospiti senza affettà u rendiment DSP.

| Specificazioni: | |

| Attributu | Valore |

| categuria | Circuiti integrati (IC) |

| Embedded - Microprocessori | |

| Mfr | Texas Instruments |

| Serie | OMAP-L1x |

| Pacchettu | vassa |

| Status di parte | Attivu |

| Processore core | ARM926EJ-S |

| Numeru di Cores / Bus Width | 1 Core, 32-Bit |

| Velocità | 456 MHz |

| Co-processori / DSP | Trattamentu di signali;C674x, Sistema di cuntrollu;CP15 |

| Controllers RAM | SDRAM |

| Accelerazione grafica | No |

| Display & Interface Controllers | LCD |

| Ethernet | 10/100 Mbps (1) |

| SATA | SATA 3 Gbps (1) |

| USB | USB 1.1 + PHY (1), USB 2.0 + PHY (1) |

| Tensione - I/O | 1,8 V, 3,3 V |

| Temperature di funziunamentu | -40 °C ~ 90 °C (TJ) |

| Funzioni di sicurezza | Boot Security, Criptografia |

| Pacchettu / Casu | 361-LFBGA |

| Paquet di Dispositivi Fornitore | 361-NFBGA (16 x 16) |

| Interfacce addiziunali | HPI, I²C, McASP, McBSP, MMC/SD, SPI, UART |

| U numeru di produttu di basa | OMAPL138 |

RelativuPRODOTTI

-

Tel

-

E-mail

-

skype

-

whatsapp

whatsapp